NUMERICAL APPROACH FOR THE PREDICTION OF FATIGUE CRACK GROWTH IN MICROELECTRONICS SOLDER JOINTS

K. Kaminishi\*, M. Iino\* and M. Taneda\*\*

A finite element analysis (FEA) program employing a new scheme for crack growth analysis is developed, FEA of fatigue crack growth in microelectronics solder joints being carried out by this program. The FEA results show that crack extension rate and path are controlled by a maximum opening stress range,  $\triangle \sigma \theta_{\text{max}}$ , at a small radial distance of r=d, where d is chosen to be a grain diameter's distance,  $3.5 \,\mu$  m, in solder material. Experimentally obtained crack extension rate is found to be related to  $\triangle \sigma \theta_{\text{max}}$  in FEA as da/dN =  $\beta \left[\triangle \sigma \theta_{\text{max}} - \gamma\right]^{\alpha}$ , where  $\alpha$  =2.0,  $\beta$  = 4.5×10-9 mm<sup>5</sup>/N<sup>2</sup> and  $\gamma$  = 98MPa are determined for all test conditions.

#### INTRODUCTION

The structural integrity of the solder joint for fine-pitch leaded surface mounted device is a major reliability concern in microelectronics packaging. Especially, the fatigue resistance of solder joint is an important concern in improving package design accuracy and efficiency. The fatigue life of solder joints may be divided into crack initiation and extension lives. As to crack initiation life, many formulae based on the Coffin-Manson's law or the modified Coffin-Manson's law have been proposed (Lau et al (1), Busso et al (2) and Shiratori et al (3)). By applying the strain range partitioning approach and a linear cumulative damage concept, and using material-dependent parameters, the authors have proposed a fatigue life prediction formula on eutectic (63Sn - 37Pb) and low melting-point (37Sn - 45Pb - 18Bi) solders, expressing number of cycles to failure as a function of cyclic frequency and equivalent

- \* Department of Mechanical Engineering, Yamaguchi University

- \*\* Department of Mechanical Engineering, Fukuyama University

inelastic strain range, which can be understood to successfully incorporate a creep damage effect (Taneda et al (4)). However, little is known about the prediction method of the crack extension life.

In this study, a FEA program employing a new scheme for crack growth analysis is developed, FEA of fatigue crack growth in microelectronics solder joints being carried out by this program. On the basis of this simulation, prediction method of crack growth life is proposed and the validity of this method is shown numerically and experimentally.

# FINITE ELEMENT MODELING AND NUMERICAL SCHEMES

### Model and Material

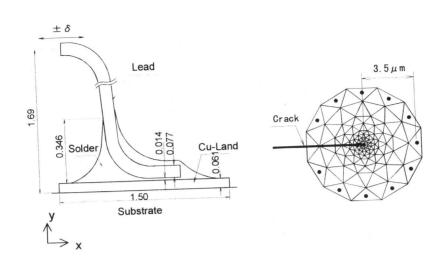

The configuration and dimension of solder joint models used in this study are shown in Fig.1. The lead wire is made of 42 Alloy, and the substrate of glass epoxy resin. In this simulation, perfect rigidity of the substrate and Cu-land is assumed, the bottom of the solder joint being constrained in the x- and y-directions. The reciprocating displacements with a constant amplitude  $\delta$  are given in the x-direction at the top of the lead wire as shown in Fig.1. To take into consideration the plasticity and creep effect, cyclic stress-strain curves obtained from fatigue test data for the bulk solder (63Sn - 37Pb eutectic solder) (Taneda et al (4)) are used.

### Crack Path Prediction

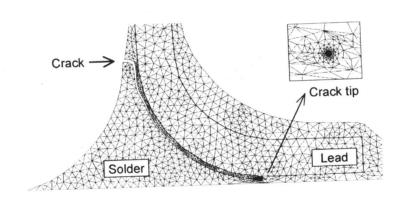

A FEA program employing a new scheme for crack growth analysis is developed, the FEA of fatigue crack growth in microelectronics solder joints being carried out by this program. The FEA program consists of the subroutines for the element configuration in the near-tip region being provided by a super-element demonstrated in Fig.3, the automatic element re-generation using Delaunay Triangulation technique (Sloan and Houlsby (5)), elasto-inelastic stress analyses, prediction of crack extension path and calculation of fatigue life. In Fig.3 bold line indicates a crack having proceeded from the left up to a current crack tip. The crack can shift its direction in accordance with the adopted fracture criterion. A crack in  $10~\mu$  m length is introduced as an initial crack at the location of numerically obtained maximum equivalent inelastic strain range.

In the process of crack growth it is found that general yielding proceeds in solder fillets. Here the linear fracture mechanics representation would be

inappropriate to describe stress fields at crack tip to determine crack extension path. It is assumed in this instance that crack extends in the direction of maximum  $\Delta \sigma_{0}$  at a small radial distance of r=d, where d is chosen to be a grain diameter's distance, 3.5  $\mu$  m, in solder material. See lino et al (6) for a theoretical account of this criteria.

## NUMERICAL RESULTS AND DISCUSSION

The FEA result using the above criteria is demonstrated in Fig 3. This figure indicates that the simulated crack extension path is in good agreement with an experimentally observed fatigue crack extension path. It would be reasonable to suppose that the crack extension path in microelectronics solder joints can be predicted by using the present FEA program.

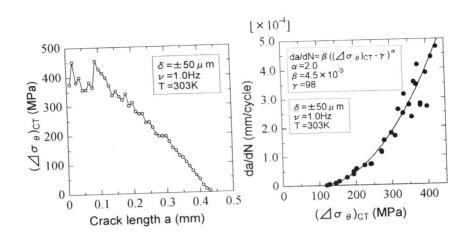

Let us now attempt to extend this simulation to the prediction of a crack extension life. The maximum  $\Delta \sigma_{\theta}$  at  $r=3.5~\mu$  m is denoted by  $(\Delta \sigma_{\theta})_{CT}$  in Fig. 4, where plot of computed  $(\Delta \sigma_{\theta})_{CT}$  versus crack length for test conditions indicated in the figure is presented. It is characteristic of this plot that  $(\Delta \sigma_{\theta})_{CT}$  decreases monotonously as crack length exceeds 0.1 mm. In Fig. 5 crack extension rate, da/dN, is plotted against  $(\Delta \sigma_{\theta})_{CT}$  which describes crack extension rate as a function of  $(\Delta \sigma_{\theta})_{CT}$  of the form for test conditions indicated in the figure

$$da/dN = \beta \left[ (\Delta \sigma_{\theta})cr - \gamma \right]^{\alpha}, \tag{1}$$

where  $\alpha=\!2.0\,,\;\;\beta=\!4.5\!\times\!10^{.9}\;mm^5/N^2\;\;$  and  $\;\gamma=98MPa.$

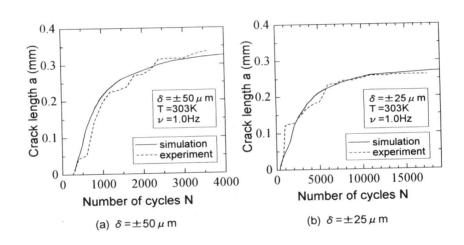

It is considered that  $\alpha$ ,  $\beta$  and  $\gamma$  in the above equation would be regarded as material constants being independent on the applied displacement amplitude,  $\delta$ , and joint type, provided that the same super-element is used in the FEA. For this reason, fatigue crack propagation life can be predicted by integrating eq.(1). Crack length-to-number of cycles relations obtained by numerical integration of eq.(1) based on the FEA are compared with experimental ones for Gullwing type joints in Fig 6. It is obvious that the FEA results employing the above equation are in agreement with experimentally observed fatigue crack extension behaviour. These comparison would suggest validity of the present FEA for the prediction of fatigue crack extension life of the solder joint.

#### **CONCLUSIONS**

A FEA program employing a new scheme for crack growth analysis is developed, the FEA of fatigue crack growth in microelectronics solder joints being carried out by this program. The FEA results show that crack extension rate and path are controlled by a maximum opening stress range,  $\triangle \sigma \theta_{\text{max}}$ , at a small radial distance of r=d, where d is chosen to be a grain diameter's distance,  $3.5 \,\mu$  m, in solder material. Experimentally obtained crack extension rate is found to be related to  $\Delta \sigma_{\theta \text{max}}$  by

$$da/dN = \beta \left[ \Delta \sigma_{\theta \max} - \gamma \right]^{\alpha},$$

where  $\alpha = 2.0$ ,  $\beta = 4.5 \times 10^{-9}$  mm<sup>5</sup>/N<sup>2</sup> and  $\gamma = 98$ MPa are determined independently of the test conditions. It is conclusively shown that the FEA results employing the above equation successfully predict are in agreement with experimentally observed fatigue crack extension path and life, thus suggesting validity of the present FEA for the prediction of fatigue crack extension life of the solder joint.

#### REFERENCES

- Lau, J.H., Rice, D.W. and Erasmus, S., Advances in Electronic Packaging 1992, ASME, EEP-Vol- 2, 1992, pp.855-865.

- (2) Busso, E.P., Kitano, M. and Kumazawa, T., ASME Journal of Electronic Packaging, Vol.116, 1994, pp.6-15.

- (3) Shiratori, M. and Qiang, Y., Fifth Intersociety Conference on Thermal Phenomena in Electronic Systems, 1996, pp.151-157.

- (4) Taneda, M. and Kaminishi, K., Advances in Electronic Packaging 1992, ASME, EEP-Vol-1, 1992, pp.337-342.

- (5) Sloan, S.W. and Houlsby, G.T., Advances in Engineering Software, Vol.6, 1984, pp.192-197.

- (6) Iino, M., Kaminishi, K. and Taneda, M., Advances in Electronic Packaging 1997, ASME, EEP-Vol- 19-2, 1997, pp.1575-1582.

Fig. 1 Geometry of test Models

Fig.2 Super-element embedded in the near crack-tip region

Fig.3 Simulated crack growth path

Fig.4 Plot of computed maximum tangential stress range against observed crack length

Fig. 5 Plot of experimentally determined crack extention rate against maximum tangential stress range

Fig.6 Relationship between crack length and number of cycles